電子回路の過去問

国試第16回午後:第13問

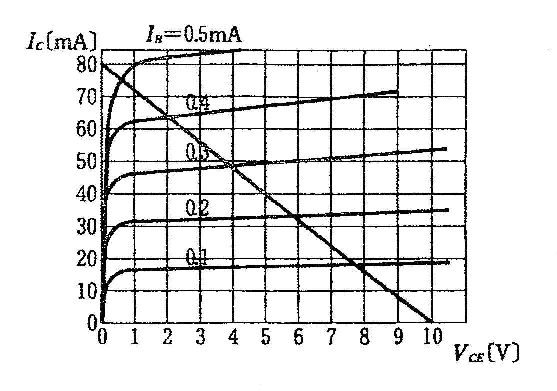

図はトランジスタの出力特性(VCE―IC曲線)とこのトランジスタを使った増幅器の負荷線を示している。ベース電流IBが0.1mAから0.2mAに変化したとき、ベース電流IBの変化量に対するコレクタ電流ICの変化量の比率に最も近いのはどれか。

1: 50

2: 150

3: 250

4: 350

5: 450

- 答え:2

- 科目:医用電気電子工学 /電子工学 /電子回路

- 重要度:集計中

- 類似問題を見る

- この問題について報告する